European Space Research and Technology Centre, Keplerlaan 12201 AZ Noordwijk, The Netherlands T +31 (0)71 565 6565F +31 (0)71 565 6040www.esa.int

# SAVOIR Flight Computer Initialisation Sequence Generic Specification

Prepared bySAVOIRReferenceSAVOIR-GS-002Issue2Revision2Date of Issue18/11/2021StatusReleasedDocument TypeGeneric Specification

European Space Agency Agence spatiale européenne

Distribution ESA Member States

Disclaimer:

ESA does not provide any warranty whatsoever, whether expressed, implied, or statutory, including, but not limited to, any warranty of merchantability or fitness for a particular purpose or any warranty that the contents of the item are error-free. In no respect should ESA incur any liability for any damages, including, but not limited to, direct, indirect, special, or consequential damages arising out of, resulting from, or in any way connected to the use of this document, whether or not based upon warranty, business agreement, tort, or otherwise; whether or not injury was sustained by persons or property or otherwise; and whether or not loss was sustained from, or arose out of, the results of, the item, or any services that may be provided by ESA.

SAVOIR documents license:

The European Space Agency, on behalf of the participating members, holds copyright for all SAVOIR documents. No SAVOIR document may be disseminated outside the ESA member states in any form without the explicit written consent of ESA via a dedicated license.

Non-ESA members states or persons from outside ESA member states willing to access or use SAVOIR documents in whole or in part in their own documentation, should file a request to ESA. Only after agreement of the SAVOIR Advisory Group, the license is signed by ESA.

#### Note that:

• direct use of SAVOIR documents themselves should be made using quotation of SAVOIR documents, rather than rewriting.

• when SAVOIR documents text is used, SAVOIR copyright is acknowledged, quotations clearly identified in the document together with exact reference/version and potential modifications of SAVOIR documents used as source.

Copyright: 2021 <sup>©</sup> by the European Space Agency

# APPROVAL

| Title                 |                 |

|-----------------------|-----------------|

| Issue 2               | Revision 2      |

| Author SAVOIR         | Date 18/11/2021 |

| Approved by           | Date            |

| SAVOIR Advisory Group | 03/12/2021      |

# CHANGE LOG

| Reason for change                                                                                                                                           | Issue | Revision | Date       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|------------|

| Prepared for Public Review                                                                                                                                  | 1     | 1        | 18/08/2015 |

| Public Review first batch of changes                                                                                                                        | 1     | 2        | 30/08/2015 |

| Public review second batch (harmonisation with GS-001)                                                                                                      | 1     | 3        | 30/09/2015 |

| Public review third version (following discussion with industry of some Rids )                                                                              | 1     | 3p       | 12/10/2015 |

| SAG endorsement review comments and editorials for publication                                                                                              | 2     | 0        | 05/04/2016 |

| Covered SoC with multiple-cores, FPGA and autonomous<br>hosted payloads. Additional IF requirements to cover<br>patch and dump operations with PUS services | 2     | 1        | 05/05/2021 |

| Public Review first batch of changes                                                                                                                        | 2     | 2        | 18/11/2021 |

# **CHANGE RECORD**

| Issue 2             | <b>Revision</b> 2 |       |              |

|---------------------|-------------------|-------|--------------|

| Reason for change   | Date              | Pages | Paragraph(s) |

| See Review RID Tool |                   |       |              |

#### Table of contents:

| 1   | Introduction                                                                                                | 6  |

|-----|-------------------------------------------------------------------------------------------------------------|----|

| 2   | Applicable and reference documents                                                                          | 7  |

| 2.1 |                                                                                                             |    |

| 2.2 | Reference documents                                                                                         | 7  |

| 3   | Terms, definitions and abbreviated terms                                                                    |    |

| 3.1 | Acronyms                                                                                                    |    |

| 3.2 | Terms and Definitions                                                                                       |    |

| 3.3 | Requirement Convention                                                                                      |    |

| 4   | Software overview                                                                                           | 12 |

| -   | Function and purpose                                                                                        |    |

|     | 1.1 Nominal Sequence                                                                                        |    |

| 4   | 1.2 Software Maintenance in Flight                                                                          |    |

|     | 1.3 Software Maintenance on Ground                                                                          |    |

| 4.2 |                                                                                                             |    |

|     | Relation to other systems                                                                                   |    |

|     | 3.1 Common HW Assumptions                                                                                   |    |

|     | <ul> <li>OBC HW Assumptions</li> <li>Payload Computer HW Assumptions</li> </ul>                             |    |

|     | Constraints                                                                                                 |    |

|     |                                                                                                             |    |

| 5   | Requirements                                                                                                |    |

| 5.1 |                                                                                                             |    |

| 5.2 | <b>Functional requirements</b><br>2.1 Nominal Sequence                                                      |    |

| -   | 2.2 Standby                                                                                                 |    |

| -   | 2.2 Standby                                                                                                 |    |

| -   | 2.4 Initialisations                                                                                         |    |

| -   | 2.5 Self-Tests                                                                                              |    |

| 5   | 2.6 Integrity tests                                                                                         |    |

| 5   | 2.7 Actions after Tests                                                                                     | 44 |

|     | Performance requirements                                                                                    |    |

|     | Boot SW related PUS System requirements                                                                     |    |

| -   | 4.1 PUS service type ST[01] Request verification                                                            |    |

|     | 4.2 PUS service type ST[03] Housekeeping                                                                    |    |

|     | 4.3 PUS service type ST[05] Event reporting                                                                 |    |

|     | <ul> <li>4.4 PUS service type ST[06] Memory management</li> <li>4.5 PUS service type ST[17] Test</li> </ul> |    |

|     | 4.6 PUS service type ST[20] Parameter management                                                            |    |

| 5.5 | Operational requirements                                                                                    |    |

| 5.6 | Resources requirements                                                                                      |    |

| 5.7 | Design requirements and implementation constraints                                                          |    |

| 5.8 | Security and privacy requirements                                                                           |    |

| 5.9 | Portability requirements                                                                                    | 59 |

| 5.1 |                                                                                                             |    |

| 5.1 | l Software reliability requirements                                                                         | 60 |

Page 4/68 Flight Computer Initialisation Sequence Generic Specification Date 18/11/2021 Issue 2 Rev 2

| 5.12   | Software maintainability requirements                                 |    |

|--------|-----------------------------------------------------------------------|----|

| 5.13   | Software maintainability requirements<br>Software safety requirements |    |

| 5.14   | Software configuration and delivery requirements                      |    |

| 5.15   | Data definition and database requirements                             |    |

| 5.16   | Human factors related requirements                                    |    |

| 5.17   | Adaptation and installation requirements                              |    |

| 6 Va   | lidation requirements                                                 | 61 |

| 7 Tr   | aceability                                                            | 61 |

| 8 Lo   | gical model description                                               | 61 |

| 9 Ho   | w to use this document                                                | 61 |

| 9.1 C  | Overview<br>Avionics and hardware environment                         |    |

| 9.2 A  | vionics and hardware environment                                      |    |

| 9.3 E  | Boot SW behavior                                                      |    |

| 9.3.1  | Boot SW behavior<br>Mode management                                   |    |

| 9.3.2  | Functionality                                                         |    |

| 9.4 T  | raceability Requirements vs variability                               |    |

| 10 Inc | dex                                                                   | 68 |

### **1 INTRODUCTION**

This document provides ESA requirements for the initialisation sequence of a typical Spacecraft On-Board Computer. The requirements are also applicable to computers belonging to other Spacecraft equipment such as mass memory, smart sensor/actuators, instruments or payloads.

The Boot SW is largely agnostic to the nominal function of the on-board unit, it deals mainly to the local processor resources, which are the same in any unit (star tracker, SSMM controller, ICU/DPU of an instrument), and any attempt to differentiate those units regarding the boot process is artificial and not necessary.

According to the hardware configuration of the targeted computer, the requirements of this document will be tailored to adjust to the hardware assumptions of section 4.3 that may be different, and the various parameters associated to some requirements (see 9 How to use this document).

Note: In the scope of the document, the term "payload computer" (as defined in 3.2) is representing any computer different from the On-Board Computer, it also covers any intelligent equipment embedding a microprocessor and running Flight SW. The main reason for this differentiation is that the OBC is the only one that can access to itself (therefore the redundancy assumption matters), whereas any other processor-based equipment can generally be accessed by the OBC.

The initialisation sequence is defined as all the operations executed by SW starting from the reset of the CPU up to the start of execution of the Application SW. This sequence can also be known as the Boot Software. For simplicity, the document shall refer to the Boot SW.

The Application SW, which is in charge of performing the mission operations, is considered an external SW item and it is not described in the present document.

The reference processor architecture used is the SPARC v7/v8, however, with exception of a few highlighted requirements, the concepts reported in the document can be applied also to other processors.

Requirements have been intentionally presented in a generic form in order not to be linked to a specific SW implementation. However, they come in the scope of the Avionics Functional Reference Architecture presented in SAVOIR-TN-001, which should be read together with this document, with the hardware assumptions specified in section 4.3.

Details not provided here, are assumed to be further specified in the project-specific boot software requirements baseline or technical specification to reflect needs and constrains given by mission, system or specific context (e.g. EDAC and interrupts enable, integrity test algorithm definition, cold/warm restart) (see 9).

# 2 APPLICABLE AND REFERENCE DOCUMENTS

# 2.1 Applicable documents

| ECSS-E-ST-40C    | Space Engineering - Software                         | 6 March 2009  |

|------------------|------------------------------------------------------|---------------|

| ECSS-Q-ST-80C    | Space product assurance - Software product assurance | 6 March 2009  |

| ECSS-E-ST-70-41C | Telemetry and telecommand packet utilization         | 15 April 2016 |

# 2.2 Reference documents

| SAVOIR-TN-001 | SAVOIR Functional Reference Architecture |              |

|---------------|------------------------------------------|--------------|

| SAVOIR-GS-001 | SAVOIR generic OBC specification         |              |

| SPARC-V8      | The SPARC Architecture Manual, Version 8 | -            |

|               |                                          |              |

| EA-2005-EEE-  | "Weak cells" in Hitachi HN58C1001 1Mbit  | 16 September |

| 09-A          | EEPROM die – ESA Alert                   | 2005         |

# **3** TERMS, DEFINITIONS AND ABBREVIATED TERMS

#### 3.1 Acronyms

| AIT    | Assembly, Integration and Test                              |

|--------|-------------------------------------------------------------|

| AOCS   | Attitude and Orbit Control System                           |

| ASW    | Application Software                                        |

| BSP    | Board Support Package                                       |

| BIT    | Built-In Test                                               |

| CAN    | Control Area Network                                        |

| CPU    | Central Processing Unit                                     |

| CRC    | Cyclic Redundancy Check                                     |

| CSW    | Central Software                                            |

| EDAC   | Error Detection And Correction                              |

| EEPROM | Electrically Erasable Programmable Read-Only Memory         |

| EGSE   | Electrical Ground Support Equipment                         |

| FDIR   | Fault Detection, Isolation and Recovery                     |

| FPU    | Floating Point Unit                                         |

| FSW    | Flight Software                                             |

| HPC    | High Priority Command                                       |

| HPC-1  | High Priority Command executed by HW without SW involvement |

| HPTM   | High Priority Telemetry                                     |

| HW     | Hardware                                                    |

| I/O    | Input/Output                                                |

| MMU    | Memory Management Unit                                      |

| OBC   | On-Board Computer                           |

|-------|---------------------------------------------|

| OS    | Operating System                            |

| PLM   | Payload Computer                            |

| PM    | Processor Module                            |

| PROM  | Programmable Read-Only Memory               |

| RAM   | Random Access Memory                        |

| RM    | Reconfiguration Module                      |

| RMAP  | Remote Memory Access Protocol               |

| SDE   | Software Development Environment            |

| SGM   | Safeguard Memory                            |

| SPARC | Scalable Processor Architecture             |

| SpW   | Spacewire                                   |

| SW    | Software                                    |

| TC    | Telecommand                                 |

| TM    | Telemetry                                   |

| TTC   | Telemetry, Tracking and Commanding          |

| UART  | Universal Asynchronous Receiver-Transmitter |

| WCET  | Worst Case Execution Time                   |

# 3.2 Terms and Definitions

| •                |                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Application      | Generic term to identify the SW charge of performing the mission                                                      |

| Software         | operations and running either on the OBC or on the Payload                                                            |

|                  | Computer.                                                                                                             |

| Application      | Read/write, non-volatile, data retention compatible with mission                                                      |

| storage memory   | availability requirements (e.g. EEPROM, FLASH).                                                                       |

| Board Support    | SW package implementing specific support code for a given                                                             |

| Package          | processor board that conforms to a given operating system.                                                            |

| Boot memory      | Read-only, non-volatile, data retention greater than mission duration (e.g. PROM, write protected EEPROM).            |

| Boot Report      | Report containing the results of the Self-Tests executed by the Boot SW. Generated by the Boot SW.                    |

| Built-In Test    | Test capability embedded in a device/equipment to autonomously verify its health status.                              |

| Cold restart     | Start of SW execution following a computer power cycle. Computer resources need to be initialised.                    |

| Central Software | Application SW running on the OBC and in charge to manage the spacecraft                                              |

| Death Report     | Report containing the ASW and processor status at the time when an unrecoverable error is detected. Generated by ASW. |

| Essential        | See High Priority Telemetry                                                                                           |

| Telemetry        |                                                                                                                       |

| High Priority    | Hardware generated telemetry that is encoded directly into the OBC                                                    |

| Telemetry        | telemetry module.                                                                                                     |

|                  |                                                                                                                       |

| Integrity test    | Test of a memory region to verify it contains the expected data or code. It is typically implemented by means of a CRC or Checksum |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------|

|                   | algorithm.                                                                                                                         |

| Interrupts        | Signals generated asynchronously with respect to the SW execution                                                                  |

|                   | by devices internal or external to the processor.                                                                                  |

|                   | Also referred as asynchronous traps.                                                                                               |

| Monitor           | SW maintenance mode on Ground.                                                                                                     |

| Nominal Sequence  | Sequence of autonomous operations leading from processor                                                                           |

| 1                 | reset/power on to ASW execution.                                                                                                   |

| On-Board          | Flight computer managing the spacecraft. It is in charge of the AOCS,                                                              |

| Computer          | the TMTC space/ground communication and the management the                                                                         |

| computer          | other subsystems.                                                                                                                  |

| Payload Computer  | Flight computer managing a specific payload subsystem. It is                                                                       |

| i dylodd Computer | typically in charge of the payload science data processing, mass                                                                   |

|                   | memory file system handling or equipment specific elaborations.                                                                    |

|                   | In the scope of the document this term also covers star trackers and                                                               |

|                   | other intelligent equipment embedding a microprocessor and                                                                         |

|                   |                                                                                                                                    |

| De et es estere   | running Flight SW.                                                                                                                 |

| Post-mortem       | Analysis of processor working memory and Death Report following                                                                    |

| investigation     | an unrecoverable error.                                                                                                            |

| Processor Module  | Module of the flight computer hosting the processor, the local                                                                     |

|                   | memories and the interfaces required to communicate with the                                                                       |

|                   | relevant equipment of the spacecraft.                                                                                              |

| Protected         | Resource (e.g. SGM) capable to retain data in case of any recoverable                                                              |

| resources         | or unrecoverable PM fault and in case of power loss.                                                                               |

| Reconfiguration   | Autonomous function implemented in HW, capable to detect                                                                           |

| function          | malfunctions (mainly) in the Processor Module and to perform                                                                       |

|                   | recovery actions in order to maintain the spacecraft in a safe state.                                                              |

| Self-Test         | Test performed autonomously during the nominal SW execution                                                                        |

|                   | with the purpose of checking the health status of a device or                                                                      |

|                   | processing resource. It could be a implemented by means of a device                                                                |

|                   | Built-In Test.                                                                                                                     |

| Standby           | SW maintenance mode in flight.                                                                                                     |

| Traps             | Exceptions generated by the execution of a processor instruction                                                                   |

| -                 | (synchronous trap) or by the detection of a transition of dedicated                                                                |

|                   | HW signals (asynchronous trap) which causes the execution of                                                                       |

|                   | specific privileged SW (trap handler).                                                                                             |

| Warm restart      | Start of SW execution following a computer reset. Some computer                                                                    |

|                   | resources (e.g. working memory) might retain information from                                                                      |

|                   | previous execution.                                                                                                                |

| Watchdog          | Autonomous timer allowing the detection of failures that prevent the                                                               |

| 0                 | nominal execution of the SW.                                                                                                       |

| Working memory    | Read/write, volatile (e.g. SRAM, SDRAM).                                                                                           |

|                   |                                                                                                                                    |

# 3.3 Requirement Convention

Requirements defined in the document are presented following the structure presented hereafter:

# SAVOIR.BOOTSW.<Function>.<Number><**Requirement Title>**

#### <Requirement text>

| Note:                  | <note text=""></note>                                                                                           |

|------------------------|-----------------------------------------------------------------------------------------------------------------|

| OptionInfo:            | < <i>EQP</i> >; < <i>EQP</i> >                                                                                  |

| Assumption:            | < Assumption>; < Assumption>                                                                                    |

| Parameter:             | <parameter>; <parameter></parameter></parameter>                                                                |

| Requirement Rationale: | <rationale text=""></rationale>                                                                                 |

| Verification Method:   | <requirement method="" verification="">; <requirement<br>Verification Method&gt;</requirement<br></requirement> |

#### where:

<Function> is an acronyms for the corresponding function amongst:

- o BEF: Boot Execution Flow

- o BIN: Boot INitialisation

- BTE: Boot Tests

- BAA: Boot Actions After tests

- BPF: Boot PerFormance

- BMM: Boot Memory Management

- IF: Interface

- IMP: IMPlementation

- STD: STanDard

<Number> is a progressive number.

<Requirement Title> is a short summary of the requirement

<Requirement Text> is the text of the requirement

<Note text> is an optional text meant to clarify or help in the interpretation of the requirement.

<EQP> is the equipment on which the requirement is applicable, amongst:

- OBC: On-Board Computer

- PLM: Payload Computer

< Assumption> is a precondition on the System and Operation for the applicability of the requirement

<Parameter> is the configuration parameter that needs to be defined in the actual project for the requirement to be applied.

<Rationale text> is the justification of the requirement

<Requirement Verification Method> is the proposed requirement verification method amongst:

- T: Validation by test;

- ROD: Validation by Review of the Design.

Page 10/68

- A: Analysis

- I: Inspection

# **4 SOFTWARE OVERVIEW**

# 4.1 Function and purpose

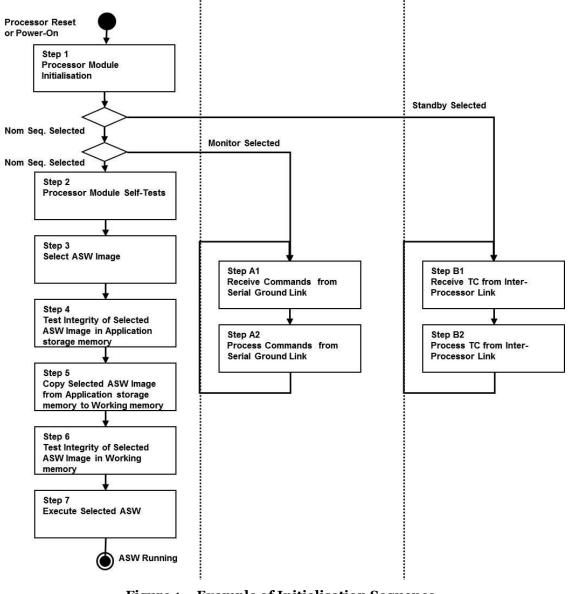

### 4.1.1 Nominal Sequence

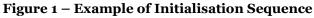

Boot SW is the first part of SW executed when a processor module is powered up or reset. It is a standalone executable typically stored in a dedicated read-only memory (Boot Memory). It is in charge to initialise and test the processor module and to execute the Application SW after copying it from a non-volatile memory area into the processing working memory.

Boot SW and ASW are independent executables with their own separate code, data, stack and trap table areas in memory.

Depending on the computer platform, execution time requirements (i.e. the time required to boot the computer and start the ASW – this is mission dependent) and SW criticality, the Boot SW can run directly from Boot Memory (slow access time) or can be copied into working memory (fast access time) and executed from there.

In some occasions, to increase flexibility in the SW development process, part of the Boot SW following the processor initialisation, might be stored and executed from Application storage memory instead of Boot Memory. This allows the possibility of later refinements/bug fixing, although if not handled with care, it leaves open the risk for an unrecoverable corruption of the Boot SW during flight.

The initialisations and Self-Tests should put the processor in condition to execute the ASW and give information of the health status of the processor module (contained in the *Boot Report*) allowing Ground to investigate the source of possible malfunctions.

The Self-Tests should be limited to the processor module functions. Any external equipment must be under the responsibility of the ASW in order to keep the Boot SW as efficient as possible. For example SGM (with the exception of the *Boot Report* area) contains the context of the ASW saved before the last reconfiguration and its content and format have meaning only to the ASW, therefore it should not be accessed or modified by the Boot SW.

It is noted that *Boot Report* should not be confused with *Death Report*. The former is produced by the Boot SW and concerns the result of the processor module Self-Tests, the latter is produced by the ASW when an unrecoverable error occurs and reports the status of the processor at the time of the failure.

The OBC Boot SW stores the *Boot Report* in the safe guard memory. It is assumed that the OBC supports this function by providing a safe memory area powered by a power line independent from the processor power supply (see also Figure 2).

In case of computer supporting multiple autonomous reboots, the *Boot Report* should be managed in such a way that important information from one reboot is not overwritten by subsequent reports.

It is assumed that more than one ASW image is available in Application storage memory. This allows to update in-flight one image in order to correct malfunctions or to improve the SW performance and still to have the possibility to roll back to a second and safe ASW image not affected by the latest patches.

A common approach is that the Boot SW selects the ASW image to load in working memory after reading status bits set by Ground via HPC-1 commands. Some more elaborated mechanisms to autonomously select the image (e.g. based on the result of the integrity tests on ASW image or segments of it) are also possible, but should be adopted only when specific mission requirements justify it (e.g. survival of the spacecraft during long periods of time without Ground contact).

In general Boot SW is not supposed to perform any recovery action following the detection of a failure in a Self-Test. This is motivated by the fact that Boot SW should have a simple design, mainly independent from the FDIR strategy defined for a given mission. Moreover, Boot SW cannot be modified in flight, therefore any autonomous recovery action implemented in it might add unnecessary constrains to spacecraft operations afterwards. The general strategy to leave FDIR out of the boot SW is still valid and generally accepted. Potential FDIR requirements would be addressed in the technical requirement specification, if needed by a specific mission and enabled by specific computer architecture. For example, the support to enable redundant memory banks depends on the computer architecture and the mission context.

Figure 2 - Nominal Sequence memory context (OBC)

On OBC, during the initialisation sequence, external watchdog is used. Under the assumption that the hardware (e.g. Reconfiguration function) will mask the watchdog for a time larger than the Boot SW typical execution, the boot software does not need to refresh

the watchdog. HW insures the masking of the watchdog for the time needed to complete the sequence. This external watchdog is reset only by ASW, therefore, lack of external watchdog kick serves as a mean for detection of ASW start-up failure.

On PLM, the CSW running on the OBC can verify the completion of the initialisation of the payload computer by checking the state transition from initialisation to nominal mode or by monitoring the telemetry event reports produced during the payload initialisation.

# 4.1.2 Software Maintenance in Flight

The Boot SW is often required to provide SW support for the maintenance in-flight of the other SW items of the flight computer (e.g. ASW). This is justified by the fact that the Boot SW is a standalone executable and it is stored in a reliable and read-only memory (opposite to patchable and less reliable non-volatile memory where the ASW is normally stored).

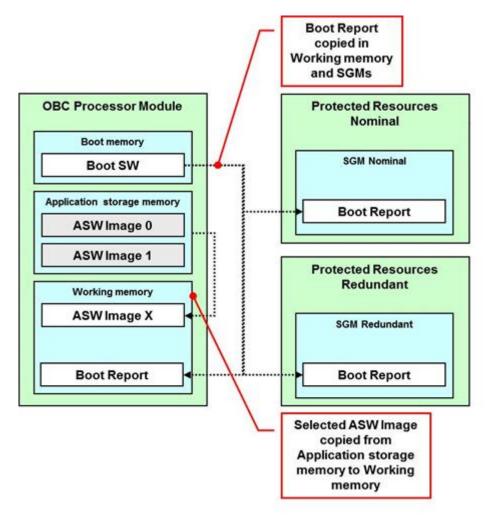

The SW is maintained in flight by means of memory patch/dump/check operations commanded from Ground and the Boot SW supporting this functionality while operating in a *Standby* mode.

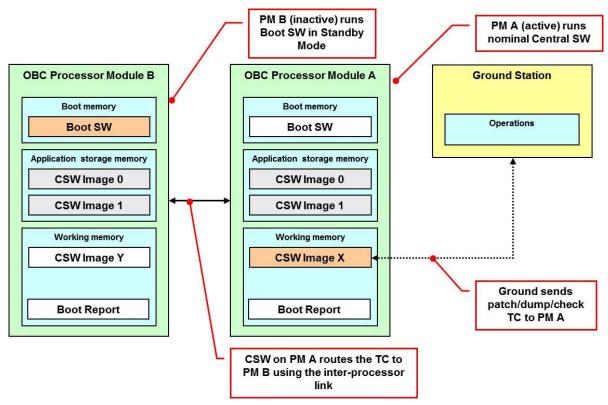

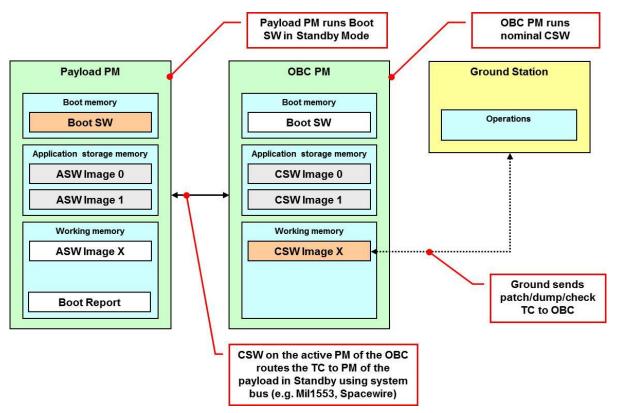

There are two main scenarios where the *Standby* mode is involved. One covers the maintenance of the SW located in one of the processor modules of the OBC (Figure 3), while the other covers the maintenance of the SW located on the processor module of a Payload Computer (Figure 4).

Figure 3 - Standby mode in OBC context

In the OBC scenario, the active processor module runs the nominal Central Software and manages the spacecraft including AOCS and TM/TC communication with Ground. The Standby mode runs on the inactive processor module that is in charge to process memory load/dump/check commands originated from Ground and routed to it by the active processor module via a dedicated inter-processor link (e.g. serial line, CAN bus, other equivalent means).

Figure 4 - Standby mode in payload computer context

In the Payload Computer scenario, the communication with Ground is usually managed by the OBC, which routes the memory load/dump/check commands to the Payload Computer using the system bus (Mil1553, Can Bus) and its related protocol. Some advanced payloads may have a direct communication link with Ground. In that case, the Standby scenario of the Payload Computer is similar to the one of the OBC.

When allowed by the mission/avionics system requirements, the communication protocol for the memory load/dump/check between OBC and Payload Computer should be kept as simple as possible, to avoid unnecessary complexity implemented in the *Standby* mode.

In both scenarios *Standby* mode could also be used to enable post-mortem dump of the working memory after processor module switch over or processor reboot, provided that the working memory banks in the faulty processor module are not switched off or erased prior to entering the *Standby* mode.

*Standby* enables the modification in flights of all other SW items and it is therefore classified as category B. Its specific characteristics depend on the computer platform and on the way the inter-processor link is implemented; however the *Standby* function should always be supported to ensure an adequate level of SW maintenance.

# 4.1.3 Software Maintenance on Ground

The Boot SW also provides SW support for the maintenance on ground of the other SW items of the flight computer.

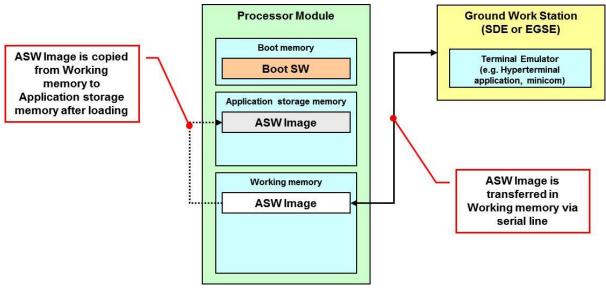

Figure 5 - Monitor context

The SW maintenance during ground operation mainly addresses SW debug or loading of the ASW image in the processor memory and it is provided by a Boot SW mode called *Monitor*. As shown in Figure 5, the *Monitor* mode supports communication between the processor located in the flight equipment and a ground workstation acting as SW Development Environment (SDE) or EGSE. *Monitor* usually has a shell-like interface requiring a simple back end on the host ground computer to interact with the operator and might have hooks to support high level debugging capabilities.

The SW criticality of the *Monitor* is lower than the rest of the Boot SW because it is used only on Ground. However, since it supports interfaces only foreseen in the ground configuration (e.g. serial line connected to the SDE), this mode should be deactivated in flight configuration and the mechanisms to start it (e.g. presence of test connector and time out on serial line) should be such that its activation will not be induced by a single failure on the computer.

The specific capabilities of the *Monitor* depend on the computer platform, but the functionality should always be present to ensure an adequate level of SW maintenance on ground. Monitor mode can be leveraged to introduce specific debugging capabilities, other than those offered by the hardware platform, when a specific debugging interface (e.g. JTAG) is not available.

In computers supporting debug capability in HW (e.g. DSU on LEON2/3 processors, SpW link with RMAP) the *Monitor* function might be embedded in the processor instead of being a SW item.

# 4.2 Environmental considerations

None.

# **4.3** Relation to other systems

A number of features presented above and further specified in the requirements section rely on HW functionalities provided by the computer platform. If some of this functionality is missing, some requirements cannot be fulfilled or will require unnecessary complexity to be added to the Boot SW.

In the following sections, a summary of the expected computer features applicable to OBC or Payload Computers is presented. These HW assumptions are preconditions for some requirements. These preconditions are highlighted when necessary in the requirements.

It is out of scope for this document to specify the HW requirements for the computer platform.

# 4.3.1 Common HWAssumptions

The following basic features are expected in both OBC and Payload Computers, in order to support the specified Boot SW functionality:

- a. Boot memory: read-only, non-volatile, data retention greater than mission duration (e.g. PROM, write protected EEPROM) to store and execute the Boot SW (or at least the initial part of it).

- b. Application storage memory: read/write, non-volatile, data retention compatible with mission availability requirements (e.g. EEPROM, FLASH) to store at least two ASW images.

- c. Working memory: read/write, volatile (e.g. SRAM, SDRAM) to execute the ASW.

- d. Capability to select the ASW image from Ground.

- e. Capability to activate the *Standby* function from Ground.

- f. *Monitor* interface for communication on Ground.

- g. In case of multicore processors, capability to run the Boot SW from one core, while the others are kept in reset state.

Note: EEPROM data retention limitations should also be considered when deciding to use EEPROM instead of PROM for Boot SW (for further details see [EA-2005-EEE-09-A]).

Note: In a multi-core processor, the boot process is done by one core (i.e. single core processor configuration). Secondary cores(s) are disabled during the entire execution of the Boot SW. Initialisation of the secondary core(s) is performed by the ASW after it is started on the primary core.

Note: System-on-Chips are embedding one or multiple processing cores tightly coupled to reprogrammable logic (FPGA). If the configuration of the FPGA is required to initialise the computer (e.g. it includes the management of interfaces), the FPGA is expected to be configured prior the initialisation of the main processing core (e.g. by loading predefined configuration). Otherwise, the initialisation of the FPGA is expected to be performed by the ASW.

# 4.3.2 OBC HW Assumptions

As already mentioned the OBC is in charge to execute the CSW including the AOCS and TM/TC space/ground communication management.

The following basic features are expected in support to the Boot SW requirements:

- a. A SW independent reconfiguration function capable to perform a recovery action (e.g. PM reset, switch over to redundant PM) in case of processor malfunctions.

- b. Interface allowing the processor module to acquire, via a local access (e.g. parallel port or register), which recovery action has been executed by the reconfiguration function.

- c. Processor module redundancy.

- d. Capability to have both nominal and redundant processor modules powered on at the same time.

- e. Protected resources (e.g. SGM) capable to retain data in case of any recoverable or unrecoverable PM fault and in case of power loss.

- f. Arbitration (and cross-strapping) allowing nominal and redundant processors to access protected resources concurrently.

- g. Capability for the nominal processor module to communicate with the redundant processor module and vice versa (e.g. inter-processor link such as UART or CAN Bus).

- h. *High Priority Telemetry* (also known as *Essential Telemetry*) accessible by SW, but generated without SW intervention.

- i. Interface allowing the processor module to check, via a local access (e.g. parallel port or register), if the processor module is set as active (i.e. executing Boot SW nominal sequence, then CSW) or inactive (i.e. executing StandBy SW).

# 4.3.3 Payload Computer HWAssumptions

The Payload Computer is a general term used in the document to identify the flight computers (different from the OBC) embedded in some of the spacecraft equipment (e.g. instruments, mass memories, star trackers) and in charge of specific functions.

Due to the difference with respected to the OBC in criticality, interfaces and redundancy, the following HW assumption(s) apply:

a. Communication link with OBC (e.g. Mil1553 Bus, UART, CAN Bus, SpaceWire).

# 4.4 Constraints

None

# 5 **REQUIREMENTS**

This section defines the minimum set of requirements applicable to every Boot SW product.

# 5.1 General

#### SAVOIR.BOOTSW.BEF.05

#### **Boot software modes**

The Boot software shall support the following modes:

- Nominal Sequence Mode, where the PM function loads an Application Software image.

- Standby Mode.

- Monitor Mode, where the PM function is controlled from a dedicated EGSE I/F.

| Note:                | In Standby mode of operation, the PM function is controlled by the active PM.                                                                                                  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OptionInfo:          | OBC; PLM                                                                                                                                                                       |

| Assumption:          | Boot memory; Application storage memory; Working<br>memory; Select ASW image from ground; Activate Standby<br>from ground; Monitor interface                                   |

| Rationale:           | Different boot modes are required for active, inactive, or<br>payload computer processor module and a Monitor mode<br>is used on ground during development and AIT activities. |

| Verification Method: | Т                                                                                                                                                                              |

# **5.2** Functional requirements

### 5.2.1 Nominal Sequence

Requirements in this section address the execution flow steps performed by the Boot SW during the Nominal Sequence.

The Nominal Sequence does not contain the activation points for *Monitor* and *Standby* modes because the precise points in the sequence where to place these checks depend on the project and equipment requirements.

#### **Boot software execution**

The Boot SW shall be executed on processor reset (power-on reset, SW reset, error reset, watchdog reset).

| Note:                | the handling of cold or warm restart conditions depend on project-specific requirements and are not described in this document.               |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| OptionInfo:          | OBC; PLM                                                                                                                                      |

| Assumption:          | Boot memory                                                                                                                                   |

| Parameter:           | ColdWarm                                                                                                                                      |

| Rationale:           | the requirement constrains Boot SW entry point and its allocation in memory (i.e. start from address 0x0000000, no other SW executed before). |

| Verification Method: | ROD; T                                                                                                                                        |

#### SAVOIR.BOOTSW.BEF.15 Fast Boot Path selection

The Fast Boot Path selection shall be based on configuration data that are set prior to the PM reset/PM power-on.

| Note:                | This can be data residing in the protected resource (SGM),<br>data set by direct telecommand or data set by the<br>Reconfiguration function. |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| OptionInfo:          | OBC; PLM                                                                                                                                     |

| Parameter:           | FastBootPath                                                                                                                                 |

| Rationale:           | Fast Boot Path is used to bypass specified Nominal<br>Sequence steps, e.g. PM Self Tests or Application Software<br>integrity check.         |

| Verification Method: | T                                                                                                                                            |

esa

#### Boot software nominal sequence

When Fast Boot Path is not selected, the Boot SW Nominal Sequence shall execute as minimum the following steps:

- 1. Perform processor module initialisations;

- 2. Perform processor module Self-Tests;

- 3. Select the active ASW image;

- 4. Test integrity of the selected ASW image in Application storage memory;

- 5. Copy the selected ASW Image from Application storage memory to processor working memory;

- 6. Test integrity of the selected ASW image in processor working memory;

- 7. Execute the selected ASW in processor working memory.

| Note:       | It is expected to have at least two ASW images for each<br>processor module. This is part of the variability expressed<br>in section 9. ASW image can include patches.<br>This mitigates limitations in Application storage memory<br>data retention and allows having one image available for<br>patching and another untouched to be used in case of<br>contingency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OptionInfo: | OBC; PLM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Note:       | In case of multi-core processors, secondary core(s) are disabled during the entire execution of the Boot SW [ SAVOIR.BOOTSW.BIN.245 ].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Assumption: | Application storage memory; Working memory; Select<br>ASW image from ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Rationale:  | <ul> <li>The requirement defines the minimal functionality:</li> <li>Processor and processor module devices need to be initialised and tested in a controlled way before being enabled.</li> <li>Most of the devices cannot be tested in the ASW context, since the I/Fs are enabled and in use. Self-Tests at initialisation time give also a higher level of confidence in the HW design/manufacturing, since the processor module devices are tested every time the equipment is powered-on.</li> <li>ASW image integrity needs to be tested in order to give information about the cause of possible malfunctions during its early execution. The checks for Standby and Monitor activation are not mentioned because they can be placed in different points of the sequence, depending on mission requirements or extra features supported by the Boot SW.</li> </ul> |

Verification Method:

Т

esa

# sa

# **Fast Boot Path sequence**

When Fast Boot Path is selected, the Boot SW Fast Sequence shall execute a subset of the step of the nominal sequence.

| Note:                | <i>The selected subset of nominal sequence's step is defined following mission constraints.</i> |

|----------------------|-------------------------------------------------------------------------------------------------|

| OptionInfo:          | OBC; PLM                                                                                        |

| Parameter:           | FastBootPath                                                                                    |

| Rationale:           | The Fast Boot path allows to reach nominal mode in a minimum time.                              |

| Verification Method: | T                                                                                               |

#### SAVOIR.BOOTSW.BEF.25 **Active ASW image selection**

The Boot SW shall be able to select the active ASW Image based on configuration data that are set prior to the processor module reset/power-on.

Note

| Note:                | In case additional on-board autonomy is required, a more<br>elaborated selection algorithm can be specified as part of<br>the mission requirements, e.g. based on the previous<br>history of spacecraft (re)configuration. |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OptionInfo:          | OBC; PLM                                                                                                                                                                                                                   |

| Assumption:          | Protected resource retaining data when fault or power loss                                                                                                                                                                 |

| Parameter:           | NumberASWimages                                                                                                                                                                                                            |

| Verification Method: | T                                                                                                                                                                                                                          |

#### Active ASW image selection configuration data

The Boot SW active ASW image selection configuration data shall be controllable by direct TC from ground or by the Reconfiguration function.

| Note:                  | Boot Mode image selection configuration data can also<br>include data to be used by the booted software image to<br>select different operating modes, like Safe Mode.                   |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OptionInfo:            | OBC; PLM                                                                                                                                                                                |

| Assumption:            | Select ASW image from ground; Reconfiguration function;<br>Reading recovery action in reconfiguration function                                                                          |

| Parameter:             | NumberASWimages                                                                                                                                                                         |

| Requirement Rationale: | Ground should always be in the position to choose<br>(override) the default ASW image to be loaded in working<br>memory, this is usually done by means of relay status set<br>by HPC-1. |

| Verification Method:   | T                                                                                                                                                                                       |

esa

# SAVOIR.BOOTSW.BEF.30 Nominal sequence when failure

The Boot SW shall execute the steps of the Nominal Sequence also in case of failure in the Self-Tests.

| OptionInfo:            | OBC; PLM                                                                                                                                                                                                                                                                     |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:                  | Additionally, since the final version of the Boot SW is<br>expected to be implemented much earlier than the<br>finalisation of the FDIR strategy system requirements, it is<br>recommended to leave to the ASW the implementation of<br>all the SW related FDIR functions.   |

| Requirement Rationale: | Self-Tests provide information about the possible cause of<br>a failure in executing the ASW, however there's always the<br>chance that the ASW can run after a Self-Test failure (e.g.<br>working memory test fails, but the failing locations are not<br>used by the ASW). |

| Verification Method:   | T                                                                                                                                                                                                                                                                            |

### 5.2.2 Standby

The requirements in the section address the Boot SW functionality required to support SW maintenance in flight.

## SAVOIR.BOOTSW.BEF.70

#### **Standby function capability**

The Boot SW shall support the following capability in flight, by means of separate equipment supporting the space-ground communication (*Standby*):

- to load, dump and check processor memories;

- to load, dump and check registers;

- to read the local Boot Report.

| Note:                  | the memory check function is meant to be equivalent to<br>PUS service 6 memory check. It is recommended to use the<br>same algorithm used in the integrity tests.                                                                                                                                                                                                                                        |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:                  | in the case of OBC, the inactive PM runs the Standby mode<br>and the active PM manages the communication with<br>Ground. The two PMs are meant to be connected via the                                                                                                                                                                                                                                   |

| Note:                  | inter-processor link.<br>in case of Payload Computer, the Payload Computer runs<br>the Standby mode and the OBC manages the<br>communication with Ground.                                                                                                                                                                                                                                                |

| Note:                  | In case of multi-core processors, secondary core(s) are<br>disabled during the entire execution of the Boot SW [<br>SAVOIR.BOOTSW.BIN.245].                                                                                                                                                                                                                                                              |

| OptionInfo:            | OBC; PLM                                                                                                                                                                                                                                                                                                                                                                                                 |

| Assumption:            | Boot memory; PM redundancy; Powering both nominal<br>and redundant; if PM redundancy, inter processor link;<br>Reading the active/inactive status by PM; if PLM, link with<br>OBC                                                                                                                                                                                                                        |

| Parameter:             | HardwarePatch                                                                                                                                                                                                                                                                                                                                                                                            |

| Requirement Rationale: | under SW maintenance the processor module can't control<br>the spacecraft orbit, attitude and pointing. For this reason,<br>a second equipment must be active and support AOCS and<br>communication with Ground. Since it is not granted that<br>the ASW can be successfully executed in case of failure, the<br>maintenance needs to rely on a simpler and more reliable<br>SW (stored in Boot Memory). |

| Verification Method:   | T                                                                                                                                                                                                                                                                                                                                                                                                        |

#### Standby function access

The Boot SW *Standby* function shall access only resources local to the processor module without interfering with the nominal spacecraft operations managed by the active PM.

| OptionInfo: OBC        |                                                                                                                                                                                                                                                          |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Requirement Rationale: | in the OBC, the Standby is executed by the inactive PM<br>while the active PM manages the spacecraft. The inactive<br>PM should not compete for spacecraft resources or<br>interfere with the nominal spacecraft operations managed<br>by the active PM. |

| Verification Method:   | ROD; T                                                                                                                                                                                                                                                   |

|                        |                                                                                                                                                                                                                                                          |

#### SAVOIR.BOOTSW.BEF.80 Standby function triggering

The Boot SW Standby function shall be triggered by the logical AND of two independent conditions.

| Note:                  | Having two conditions to activate the Standby makes the system single point failure tolerant.                                                                                                                                  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OptionInfo:            | OBC                                                                                                                                                                                                                            |

| Parameter:             | StbyTrigger                                                                                                                                                                                                                    |

| Requirement Rationale: | Standby is normally an infinite loop waiting for commands<br>sent via the inter-processor link. On OBC, if activated in<br>flight on the active processor module, it will prevent to<br>execute the ASW (i.e. AOCS/safe mode). |

| Verification Method:   | T                                                                                                                                                                                                                              |

# SAVOIR.BOOTSW.BEF.90 Standby function activation condition

The Boot SW *Standby* activation condition shall be checked within the Boot SW Nominal Sequence.

| Note:                  | The requirement is not applicable if an automatic HW activation condition is foreseen.                                                                                                                                                                          |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:                  | If the Standby is implemented in HW, its activation might<br>not be under SW control, in this case the requirement is not<br>applicable.                                                                                                                        |

| OptionInfo:            | OBC; PLM                                                                                                                                                                                                                                                        |

| Parameter:             | StbyTrigger                                                                                                                                                                                                                                                     |

| Requirement Rationale: | the requirement constrains the designer to define a point in<br>the Nominal Sequence where the double activation<br>condition is checked. This allows a deterministic behaviour<br>of the Boot SW in the execution of the nominal and non-<br>Nominal Sequence. |

| Verification Method:   | T                                                                                                                                                                                                                                                               |

#### SAVOIR.BOOTSW.BEF.95 Standby function activation

The Boot SW shall activate the *Standby* function based on conditions controlled by Ground.

| Note:                  | Activation conditions are based on external conditions set by Ground (e.g. relay status set by HPC-1).             |

|------------------------|--------------------------------------------------------------------------------------------------------------------|

| Note:                  | The requirement is not applicable if an automatic HW activation condition is foreseen.                             |

| OptionInfo:            | OBC; PLM                                                                                                           |

| Assumption:            | Activate Standby from ground                                                                                       |

| Parameter:             | StbyTrigger                                                                                                        |

| Requirement Rationale: | Standby is used by Ground for SW maintenance, therefore the activation conditions have to be under Ground control. |

| Verification Method:   | T                                                                                                                  |

## SAVOIR.BOOTSW.BEF.97 Standby function when failure

If activated after the Self-Tests, the Boot SW StandBy function shall be executed also in case of failure in the Self-Tests.

| Note:                  | Since the final version of the Boot SW is expected to be<br>implemented much earlier than the finalization of the FDIR<br>strategy system requirements, it is recommended to leave<br>to the ASW the implementation of all the SW related FDIR<br>functions.                                            |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OptionInfo:            | OBC; PLM                                                                                                                                                                                                                                                                                                |

| Requirement Rationale: | Self-Tests provide information about the possible cause of a<br>failure in executing the ASW. However, there's always the<br>possibility that the StandBy function is executed after a<br>Self-Test failure (e.g. working memory test fails, but the<br>failing locations are not used by the StandBy). |

| Verification Method:   | T                                                                                                                                                                                                                                                                                                       |

#### 5.2.3 Monitor

The requirements in the section address the Boot SW functionality required to support SW maintenance on ground.

#### SAVOIR.BOOTSW.BEF.40

#### Monitor function capability

The Boot SW shall support the capability to load and dump memories and registers, start and halt software execution, and reset the PM on Ground command (Monitor).

| Note: More functions may | be specified in the actual project specification.                                                                                                                                                                                                                                |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OptionInfo:              | OBC; PLM                                                                                                                                                                                                                                                                         |

| Assumption:              | Monitor interface                                                                                                                                                                                                                                                                |

| Parameter:               | HardwareMon; MonFunctions                                                                                                                                                                                                                                                        |

| Requirement Rationale:   | in an embedded computer, the most common way to<br>upload the SW in Application storage memory is with the<br>support of a resident SW (i.e. stored in Boot Memory). For<br>mass and cost reasons the Monitor is stored in the same<br>memory area (Boot Memory) of the Boot SW. |

| Verification Method:     | T                                                                                                                                                                                                                                                                                |

# SAVOIR.BOOTSW.BEF.50 Monitor function triggering

The Boot SW *Monitor* function shall be triggered by the logical AND of two independent conditions.

| Note:                  | the two activation conditions should be independent from<br>the failure propagation point of view (e.g. one HW<br>condition and one SW condition).                                                                                                  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OptionInfo: OBC; PLM   |                                                                                                                                                                                                                                                     |